University: Rajasthan Technical University

Course: B.Tech Computer science & engineering

Subject: CAD for VLSI Design

Exam Year: May/June 2010

Year or Semester: Fourth year/ Eight Semester

Paper Code: 8E4015

Unit-I1. a) Explain the concept of Computer Aided design (CAD) in modern digital system with the help of a flow diagram. [Marks 8]

b) What do you understand by ASIC design? Explain the ASIC design flow with the help of a flow chart. [Marks 8]

OR

2. a) Describe the following terms in connection with Computer Aided Design (CAD) process.

i) Design Entry

ii) Simulation of a design

iii) Synthesis of a Design

iv) Optimization of a design. [Marks 8]

b) Field Programmable Gate Arrays (FPGA) are used for hardware design implementation frequently in VLSI devices. Describe the logic block (LB), switching block (SB) and input/output block (I/O B) of an FPGA. Also explain the advantages of FPGA implementation over conventional methods. [Marks 8]

Unit-II

3. a) When was the language VHDL standardized and by whom? Give the basic requirements of VHDL. [Marks 8]

b) Describe and write the syntax for the following in connection with VHDL.

i) Architecture

ii) Package

iii) Signals and variables

iv) 9-value package. [Marks 8]

OR

4. a) Describe the following terms in VHDL.

i) Modes used in VHDL

ii) VHDL system

iii) Data types

iv) Predefined enumeration data types. [Marks 8]

b) Write the VHDL code for a D flip flop. [Marks 8]

Unit-III

5. a) Describe the various types of operators used in VHDL modeling. [Marks 8]

b) Write the VHDL code for a half adder circuit using all the three types of modeling. [Marks 8]

OR

6. a) Give the syntax and the example for the following:

i) Process statement

ii) Case statement

iii) NULL statement

iv) With-select statement [Marks 8]

b) Write the VHDL code for a full adder circuit using structural modeling. [Marks 8]

Unit-IV

7. Write short notes on the following:

a) Predefined attributes and user defined attributes.

b) VHDL subprogram parameters types and overloading. [Marks 8*2=16]

OR

8. Explain the following with suitable examples.

a) Component declaration and component specification.

b) Functions and procedures. [Marks 8*2=16]

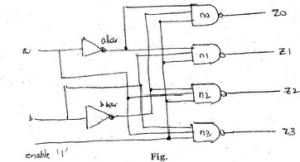

b) Write the VHDL code for 2*4 decoder. Circuit of decoder is given below. [Marks 8]

OR

10. a) Draw the state machine diagram and write the VHDL code for a “110” string detector. [Marks 8]

b) Write the VHDL code for a 4-bit compartor circuit. [Marks 8]

Return to Question Paper